In an interview with The Hypervisor, Alan Priestley, Intel Enterprise Marketing Manager, said, “The Xeon 7500 is the biggest impact we’ve made to the server platform since we launched the Xeon in 1996. It’s a huge step forward.”

It’s the first time Intel’s multi processor (MP) server chips have used the NUMA architecture. This one change means you can now buy x86 and x64 servers with a practically unlimited number of CPUs and RAM.

Priestley told The Hype, “The Xeon 7500 replaces the 7400 product line, which used a Front Side Bus (FSB) architecture. The Xeon 7500 uses an integrated memory controller and NUMA architecture, which gives an 8x bandwidth increase, due to additional memory channels and integrated memory controller. It’s the first time we’ve used NUMA in the MP product lines.”

Intel’s previous FSB designs also limited servers to a maximum four CPUs. Although third party manufacturers could develop custom hardware to support more CPUs, the custom hardware made them very expensive and performance was often disappointing.

But the new NUMA architecture used by the Xeon 7500 Nehalem EX series chips, launched today, means each CPU includes its own memory controller with four memory channels, each of which can be connected to four DIMM sites, giving each chip a maximum capacity of 16 DIMM sites.

Priestley said, “The majority of the market for Nehalem EX will be four socket servers or above. Multiple server manufacturers will offer large system with four, eight and sixteen CPU sockets, and in some cases greater.”

Other key points about the Xeon 7500 Nehalem EX chips are its new CPU micro architecture, which should help software to run faster and make the chips more energy efficient. The chips also include 20 new features to improved reliability, availability and serviceability (RAS).

“The biggest RAS feature we’ve added is the advanced Machine Check Architecture, so if a failure happens we can flag that to the operating system and the OS can decide how to handle it. It’s the first time we’ve done this in the x86 family, although we’ve had something similar in the Itanium line for some time,” said Priestley.

Of all the things MCA could help with, failures in RAM chips are the most likely. Current ECC RAM automatically handles a “single bit failure”, where an error occurs affecting a single binary digit (bit). However, ECC cannot handle errors affecting two or more bits. Priestley said such errors are increasingly likely as the amount of RAM fitted in a server gets bigger. “Now if the OS sees a 2 bit error in an area that doesn’t matter it can map it out and carry on. If it’s in a single virtual machine it might shut down that VM without affecting other workloads,” he added.

New RAS features also enable upgrades of systems without shutting them down.

Intel today also launched the Xeon 6500, which is identical to the 7500 except it can be used only in dual processor systems and will cost slightly less.

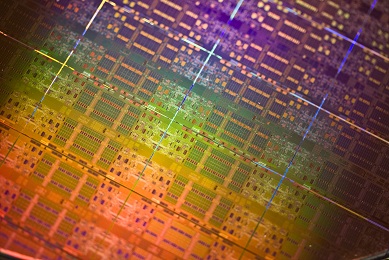

The Xeon 6500 and 7500 contain 2.3 billion transistors, and the new architecture is expandable to include from two to 256 chips per server.